【FPGA干货】详解高速ADC的串行LVDS数据捕获与接口设计

【FPGA干货】详解高速ADC的串行LVDS数据捕获与接口设计

前言

在现代高速数据采集系统中,随着ADC采样率的不断提升(从几十MHz到几百MHz甚至更高),传统的并行CMOS/LVDS接口因占用引脚过多、布线困难等问题逐渐被串行LVDS接口取代。TI(德州仪器)的许多多通道ADC(如ADS528x, ADS529x系列)都采用了这种接口。

然而,串行LVDS接口虽然减少了PCB走线数量,却给FPGA接收端的设计带来了巨大的挑战:如何在几百Mbps甚至Gbps的速率下,稳定地实现位同步(Bit Alignment)和帧同步(Frame Alignment)?

1. 认识串行LVDS接口

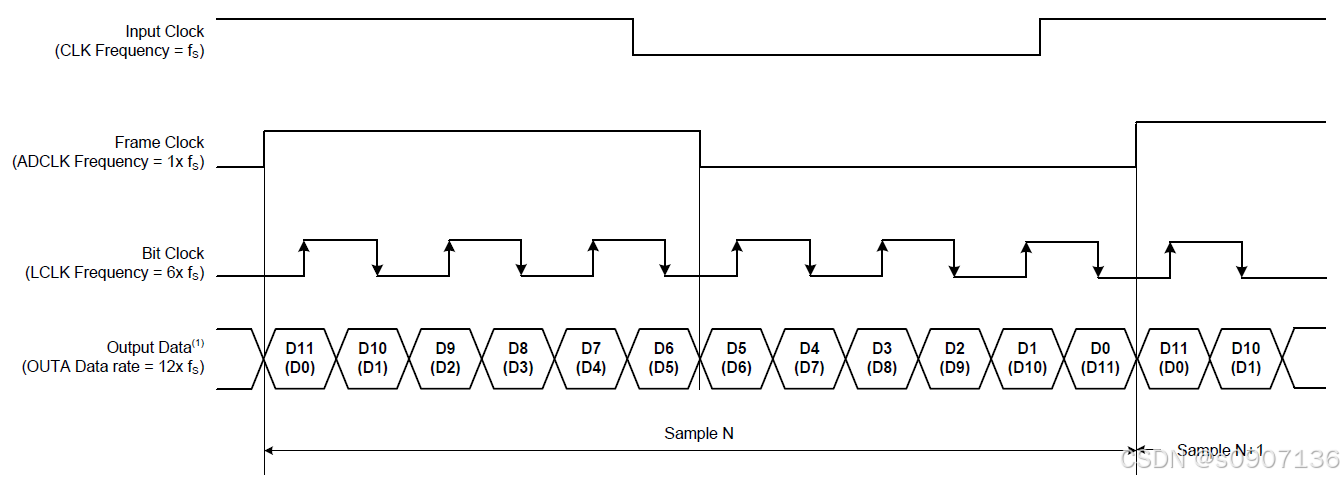

一个典型的高速ADC串行LVDS接口通常包含以下三类信号:

- 串行数据 (Serial Data, D0…DN−1D_0 dots D_{N-1}D0…DN−1):ADC的采样数据通过一对或多对LVDS线串行输出。

- 位时钟 (Bit Clock, LCLK/DCLK):通常是DDR(双沿采样) 格式。频率通常是

采样率 × 串行化倍数 / 2。 - 帧时钟 (Frame Clock, ADCLK/FCLK):频率等于ADC的采样率 (fSf_SfS)。它的上升沿通常与串行数据的第一个bit(或字边界)对齐,用于辅助并行数据的恢复。

接口变种:

- One-wire interface:每个ADC通道只需一对LVDS传数据(速率高)。

- Two-wire interface:采样率极高时,每个通道的数据拆分到两对LVDS上传输(降低单线速率)。

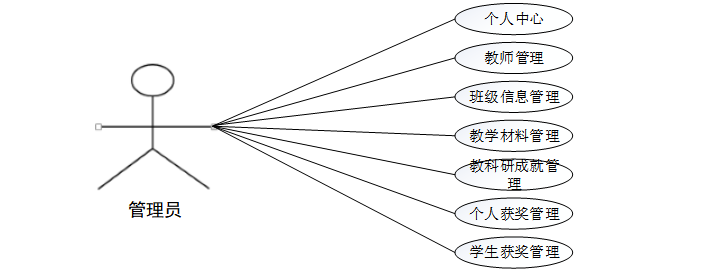

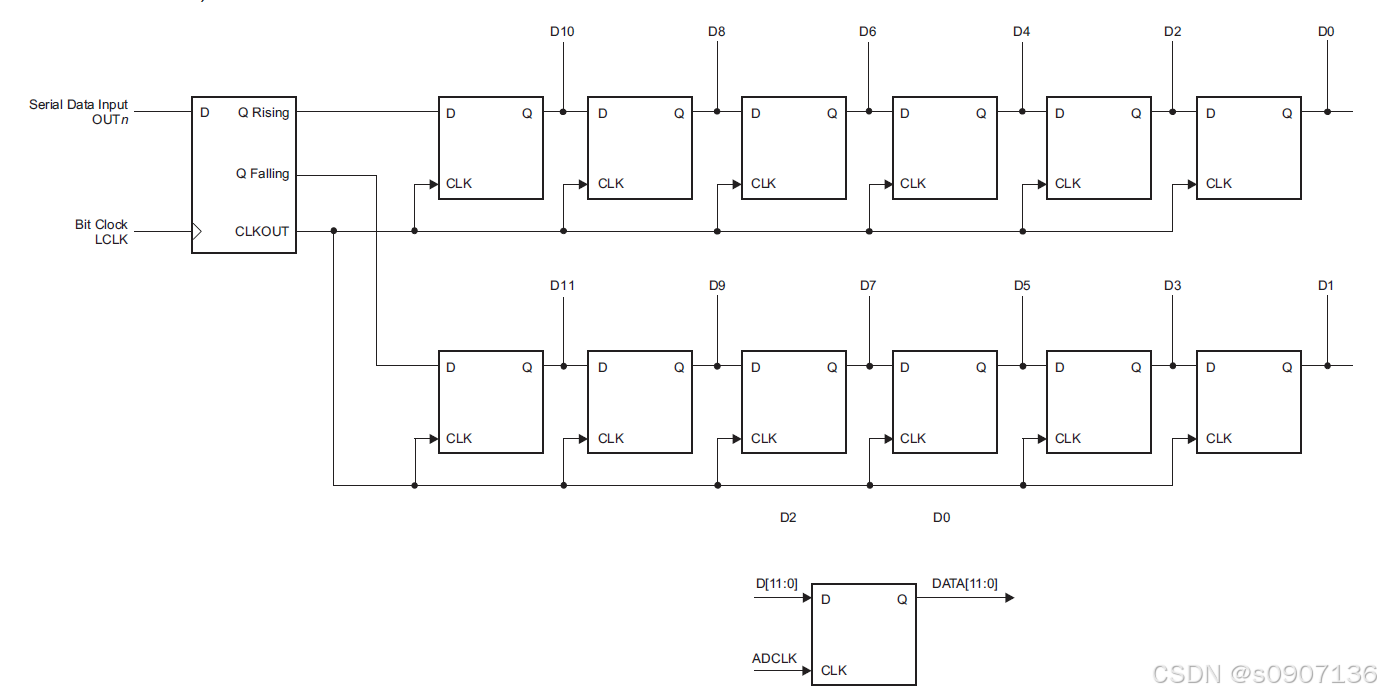

2. 接收端捕获方案 (Receiver Capture Schemes)

FPGA接收端的核心任务有两个:

- 位同步:利用位时钟(Bit Clock)正确锁存高速串行数据。

- 字/帧对齐:利用帧时钟(Frame Clock)恢复出正确的并行数据字。

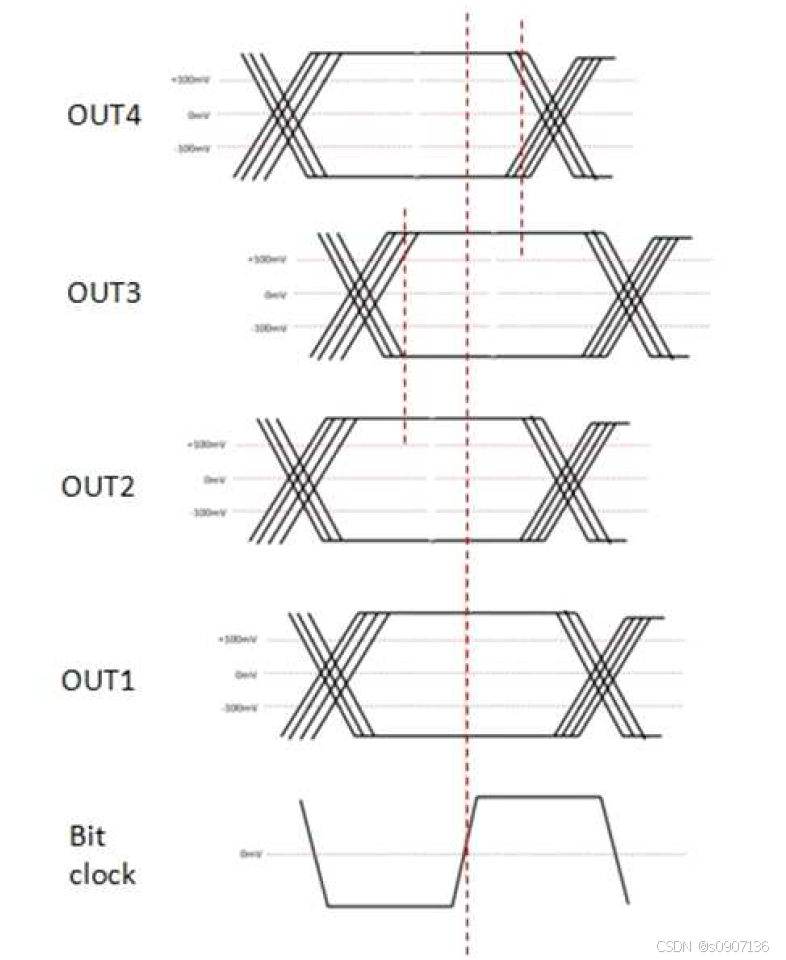

2.1 难点:时钟与数据的偏斜 (Skew)

在理想情况下,数据边缘和时钟边缘是对齐的。但在实际硬件中,PCB走线延时、FPGA内部布线延时、以及器件本身的Skew,会导致数据和时钟无法满足建立/保持时间(Setup/Hold Time)。

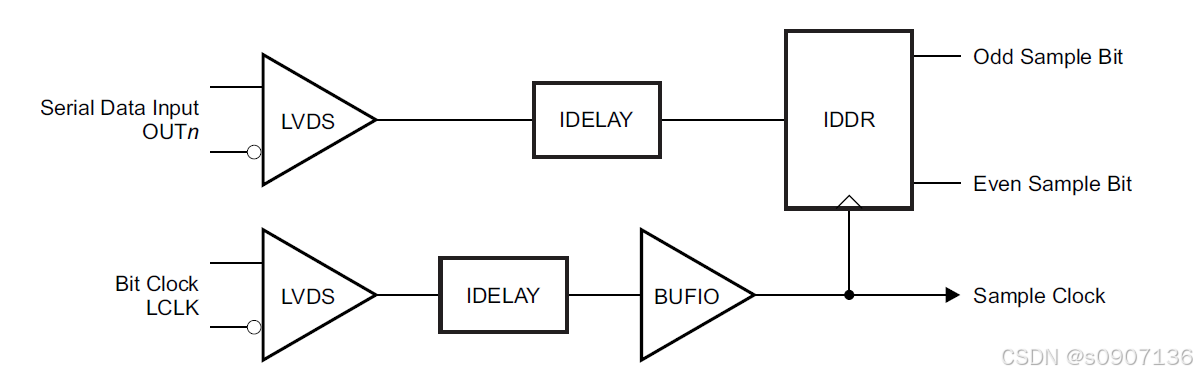

2.2 解决方案一:使用延迟元件 (Delay Elements)

- 原理:利用FPGA内部的IO延迟模块(如Xilinx的IDELAY),对输入的位时钟或数据进行微调。

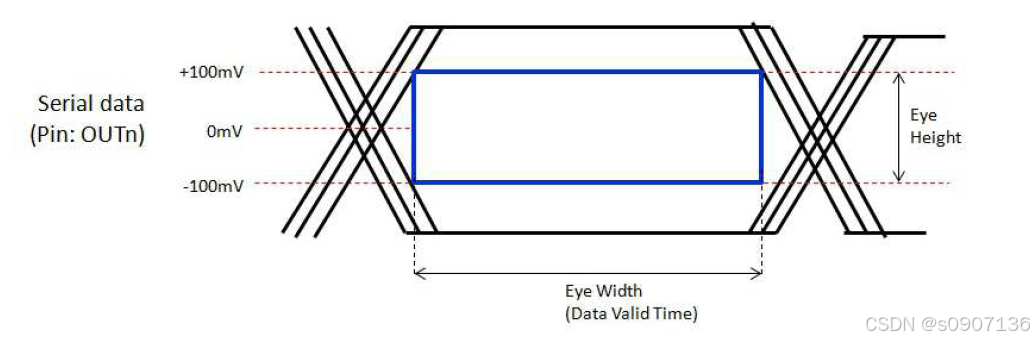

- 实现:通过动态调整延迟,使时钟沿落在数据“眼图”的中心。

- 注意:需考虑PVT(工艺、电压、温度)变化对延迟Tap精度的影响。

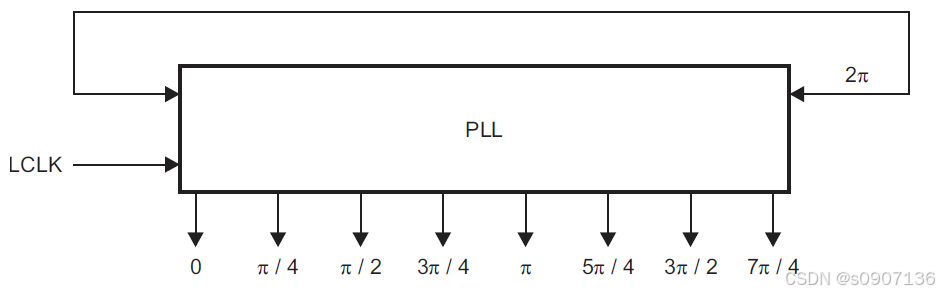

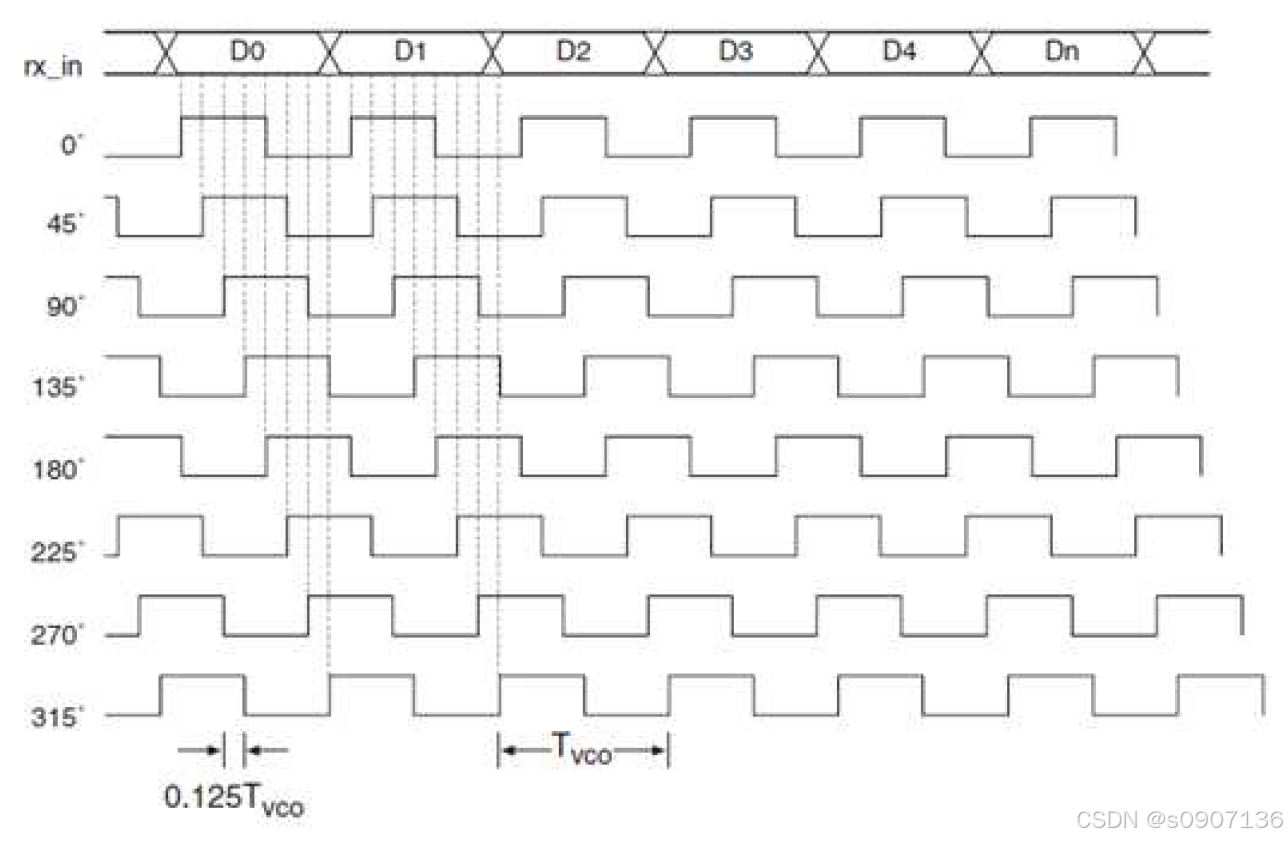

2.3 解决方案二:使用PLL多相时钟

- 原理:利用FPGA的PLL生成多个相位的时钟(例如0°, 45°, 90°… 315°)。

- 边缘选择逻辑:ADC发送Deskew Test Pattern(通常是

101010...)。FPGA用所有相位的时钟去采样,找出能稳定采到正确数据的相位窗口,并选择窗口中间的那个时钟相位作为采样时钟。

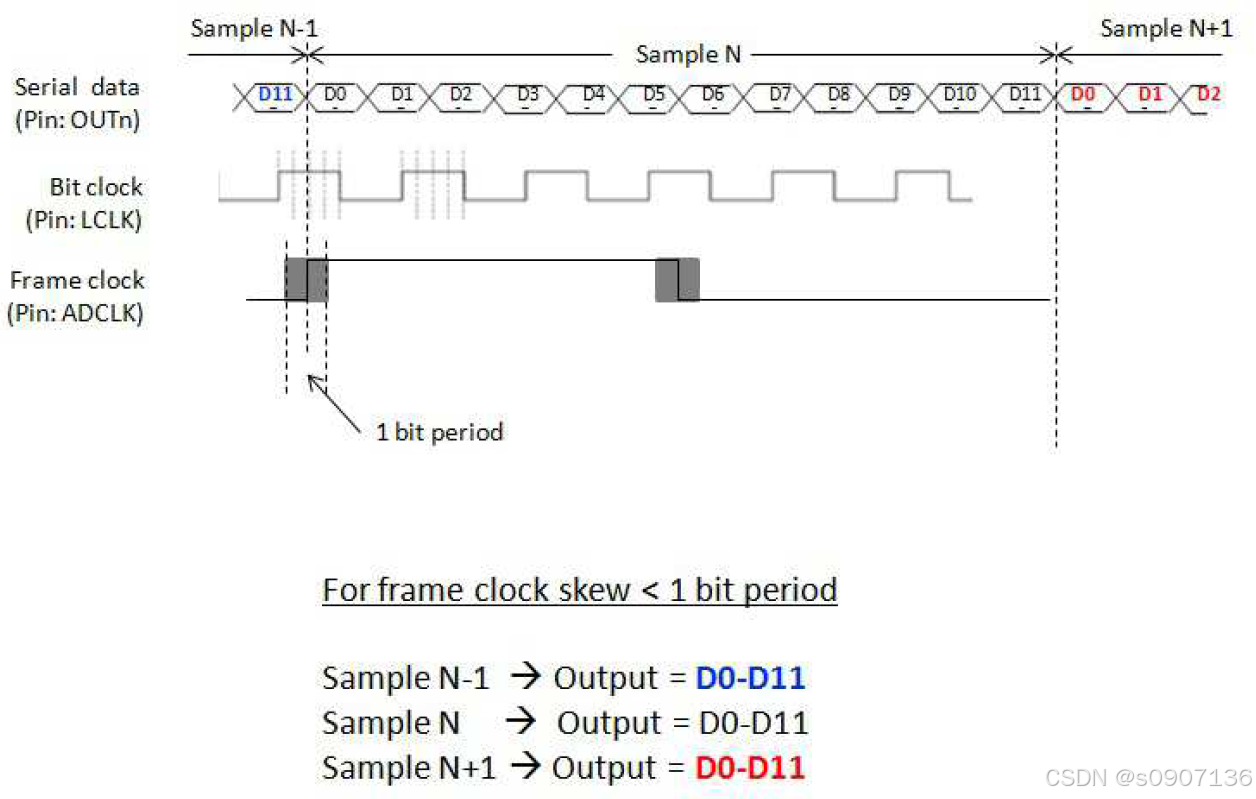

3. 帧对齐逻辑 (Frame Alignment)

即使位数据捕获正确,并行转换后的数据可能依然是错位的(Bit Shifted)。例如12-bit数据,你可能采到了上一个样本的最后1位和当前样本的前11位。

3.1 帧时钟的作用

理想情况下,直接用帧时钟(Frame Clock)去锁存串转并后的数据即可。但如果帧时钟相对于数据有较大的滞后或超前(超过1个Bit周期),就会导致错位。

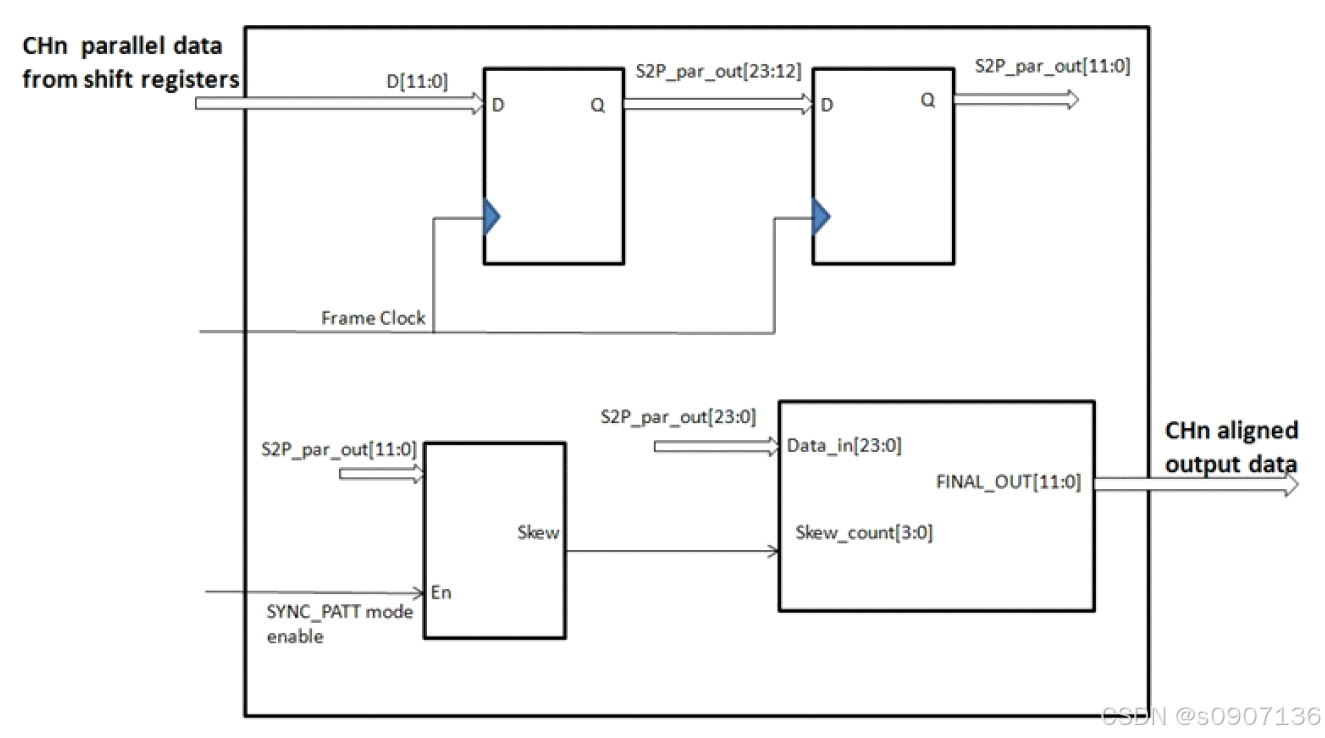

3.2 使用SYNC Pattern进行校正

TI ADC通常提供 SYNC Test Pattern(例如12-bit模式下发送 111111000000)。

- 校准流程:

- 开启ADC的SYNC模式。

- FPGA检查接收到的并行数据。

- 如果读到

111111000000,说明对齐正确。 - 如果读到

011111100000(右移)或111110000001(左移),则说明存在错位。 - 位滑移 (Bit Slip):在串转并模块中控制逻辑进行移位操作,直到数据匹配标准图案。

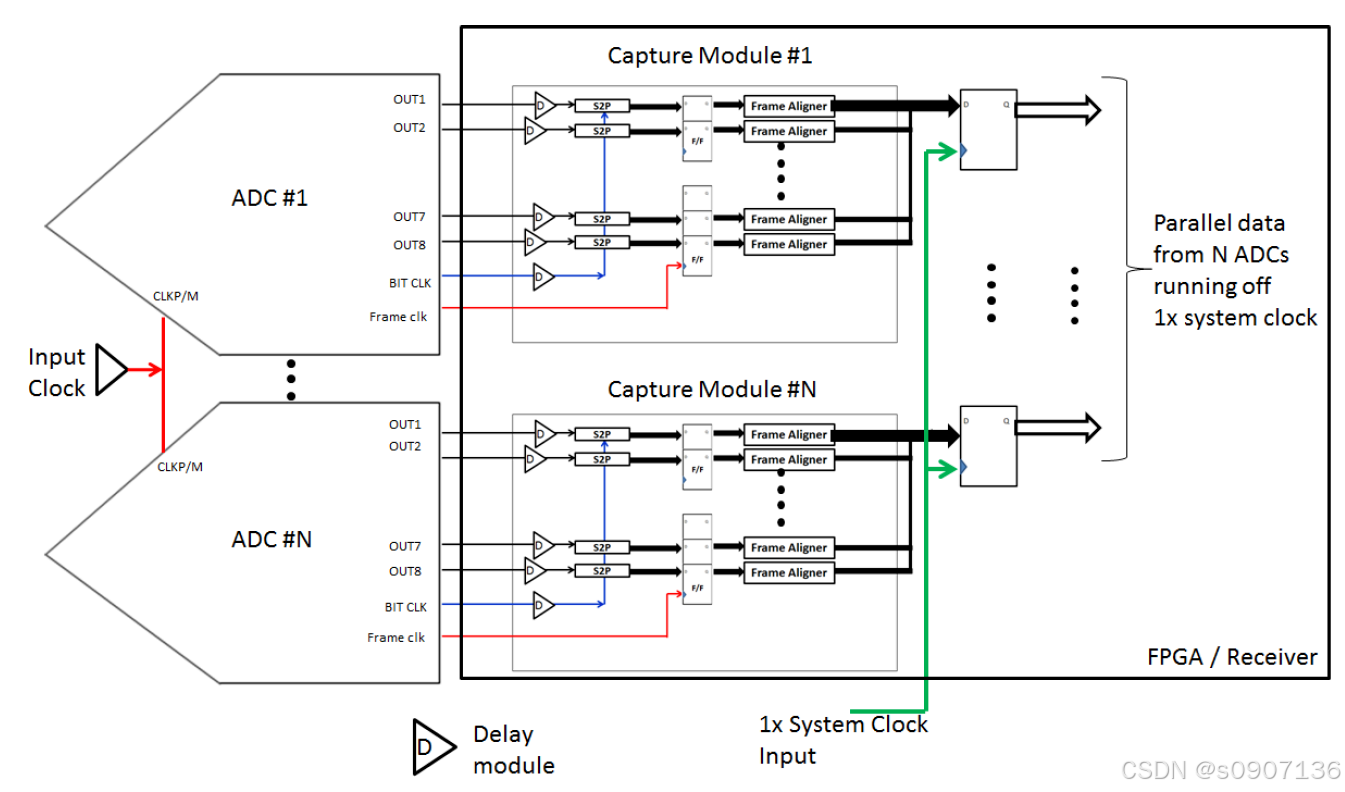

4. 多通道/多片ADC系统的同步策略

在由多片ADC组成的大型系统中,TI推荐采用 源同步(Source Synchronous) 策略:

- 独立捕获:FPGA内部为每一片ADC(甚至每个通道组)实例化独立的捕获模块。

- 使用各自的位时钟:千万不要试图用同一个时钟去采集所有ADC的串行数据。每片ADC输出的Bit Clock与它自己的Data是相关性最好的。

- 跨时钟域处理:

- 在捕获模块内部,使用ADC自己的Bit Clock恢复出并行数据。

- 恢复出的并行数据(低速)再通过FIFO或寄存器跨时钟域同步到FPGA的全局系统时钟(System Clock, 1x 采样率)。

5. 时序闭合与PCB设计 (Timing Closure)

要实现稳定的数据捕获,必须满足接收端触发器的建立时间 (tsut_{su}tsu) 和保持时间 (thot_{ho}tho)。

5.1 关键公式

接收端的实际建立时间计算如下:

tsu_RX=tsu_ADC−tSkew t_{su_RX} = t_{su_ADC} - t_{Skew} tsu_RX=tsu_ADC−tSkew

其中 tSkewt_{Skew}tSkew 是数据路径延时与时钟路径延时的差值。

tSkew=tData_Delay−tClock_Delay t_{Skew} = t_{Data_Delay} - t_{Clock_Delay} tSkew=tData_Delay−tClock_Delay

为了最大化接收端的建立时间余量,必须让 tSkewt_{Skew}tSkew 尽可能小。

5.2 PCB Layout 黄金法则

- 等长布线:对于速率 > 500 Mbps 的接口,TI建议数据线和位时钟线的长度匹配误差控制在 100 mils (约2.54mm) 以内。

- 这将由于PCB走线引起的Skew控制在 15ps - 20ps 级别,从而保留最大的时序裕量。

6. 深入理解:源同步接口与抖动 (Jitter)

为什么一定要用ADC输出的位时钟(LCLK)?能不能用FPGA自己的同频时钟?

答案是:尽量不要。

- 相关抖动 (Correlated Jitter):ADC输出的数据和时钟是从同一个内部源产生的。电源噪声引起的抖动在数据和时钟上是同向的(例如:数据延后了,时钟也跟着延后)。

- 抖动抵消:当我们用ADC的LCLK去采ADC的Data时,这种相关的抖动会被互相抵消,从而得到一个非常张开的眼图(Wide Eye)。

- 非相关抖动:如果使用外部时钟或FPGA内部时钟,由于它与ADC数据没有抖动相关性,所有的抖动都会直接吃掉建立/保持时间,导致眼图闭合,误码率上升。

总结

设计高速ADC的串行LVDS接收接口时,请遵循以下步骤:

- 硬件设计:严格保证LVDS差分对的等长匹配(特别是Data与Bit Clock之间)。

- FPGA逻辑:使用

IDELAY或PLL动态调整相位。 - 训练流程:

- 上电复位。

- 发送 Deskew Pattern (101010...101010...101010...) -> 锁定最佳采样时钟相位。

- 发送 SYNC Pattern (111111000000111111000000111111000000) -> 锁定字边界(Frame Alignment)。

- 切换回正常数据模式。

- 多片同步:坚持“独立捕获,后端对齐”的原则。

参考资料:Texas Instruments Application Report SBAA205 - Understanding Serial LVDS Capture in High-Speed ADCs